### 発明の名称

# 半導体メモリセル構造及び半導体記憶装置

~装置の小型化が可能な半導体メモリセル構造の構築技術~

#### 発明者

武山 真弓、佐藤 勝 (北見工業大学)

技術概要

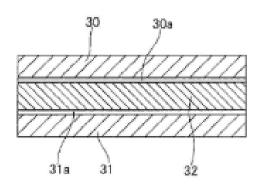

この発明の半導体メモリセル構造は、第1の電極層と第2の電極層、これらの電極層間に積層された化合物層、いずれか一方の電極層と化合物層が接する界面部に形成された金属酸化物を備えます。例として、電極層に銅、化合物層に窒化ジルコニウム、界面部の金属酸化物に酸化銅を備えることで、化合物層と電極層の間で抵抗変化が生じてメモリ機能が得られ、さらに界面部で整流機能が得られます。この構造のメモリセル、記憶装置により、消費電力の低減や装置の小型化が期待できます。

### 発明の目的

単純な構造を有し、回路面積が増大しない半導体メモリセル構造、半導体記憶装置を得ることを目的とし、さらに材料や製造における低コスト化も可能にすることです。

# 効果

一方の電極層の界面に整流機構を作成することで回路面積の増大を回避し、単純な構造で整流機能とメモリ機能を同一セル内で実現できる。また、新たな材料を付加せずに電極材料を使用でき、電極材料を酸化処理する方法により製造工程を簡略化できます。

#### 図面

### 詳細はこちら

工業所有権情報・研修館のサイトに移動します

## 出願・登録

| 出願日        | 設定登録日      | 存続期間満了日    |

|------------|------------|------------|

| 2020/02/18 | 2023/09/01 | 2040/02/18 |